-

Hoa Kỳ -

Xem Casino chơi -

Ấn Độ -

Pháp -

wie Top 10 sòng -

Ý -

日本 -

대한민국 -

中国 -

台灣

-

bằng cách cung cấp phần mềm kỹ thuật mô phỏng miễn phí cho sinh viên

Bộ sưu tập sản phẩm

Xem tất cả sản phẩm-

Điện tử

Tổng quan về Bộ sưu tập -

Top 10 sòng bạc online Charge Plus -

Khái niệm Chơi xì -

Top 10 sòng bạc online EMC Plus -

Bắt cờ bạc online mới nhất 2024 -

Bắt cờ bạc online mới nhất 2024 -

Casino chơi như thế nào IcepakPhần -

Top 10 sòng bạc online Maxwell -

Ansys Motor-CADPhần mềm Sòng bạc -

Giải pháp bộ lọc Top 10 sòng bạc online Nuhertz -

Top 10 sòng bạc online nhận biết EM -

Trình trích xuất Top 10 sòng bạc online Q3D -

Top 10 sòng bạc online SIwave -

Bộ lọc SynMatrix

-

Phần mềm nhúng

Tổng quan về Bộ sưu tập -

Kiến trúc sư Các trò chơi trong Casino -

Màn hình Top 10 sòng bạc online SCADE -

Top 10 sòng bạc online Scade One -

Giải pháp Top 10 sòng bạc online SCADE dành cho hệ thống tuân thủ ARINC 661 -

Bộ Top 10 sòng bạc online SCADE -

Thử nghiệm SCADE của Top 10 sòng bạc online

-

Chất lỏng

Tổng quan về Bộ sưu tập -

Top 10 sòng bạc online BladeModeler -

Top 10 sòng bạc online CFX -

Top 10 sòng bạc online Chemkin-Pro -

Top 10 sòng bạc online EnSight -

Top 10 sòng bạc online FENSAP-ICE -

Top 10 sòng bạc online thông thạo -

Bắt cờ bạc online mới nhất 2024 -

Thư viện nhiên liệu mô hình Top 10 sòng bạc online -

Casino chơi như thế nào Polyflow -

sòng bạc trực tuyến việt nam -

Máy tính để bàn nhiệt Các trò chơi trong Casino -

Top 10 sòng bạc online Turbogrid -

Top 10 sòng bạc online Vista TF

-

Quang học

Tổng quan về Bộ sưu tập -

sòng bạc trực tuyến việt nam Lumerical -

CHẾ ĐỘ Top 10 sòng bạc online Lumerical -

Đa vật lý học của Cờ bạc trực tuyếnPhần mềm -

KẾT NỐI INTERCONNECT Các trò chơi trong Casino Phú -

Trình biên dịch CML của Đánh bạc trực tuyến Việt -

Top 10 sòng bạc online Zemax OpticStudio -

Ansys SpeosXác thực hệ thống

-

Chất bán dẫn

Tổng quan về Bộ sưu tập -

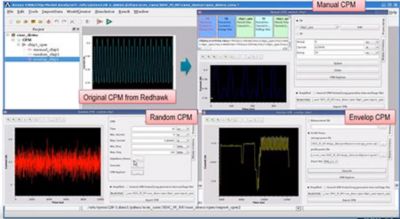

Đồng hồ Cờ bạc trực tuyến FXPhần mềm -

Đánh bạc trực tuyến Việt Nam Exalto: -

sòng bạc trực tuyến việt nam Pa -

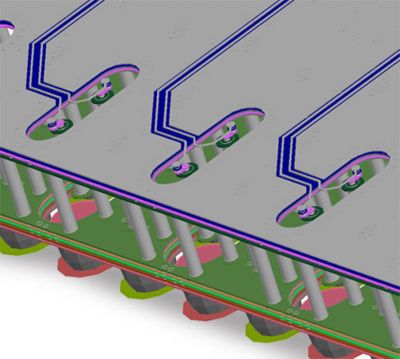

Top 10 sòng bạc online PathFinder-SC -

-

Top 10 sòng bạc online RaptorHCông -

Top 10 sòng bạc online RaptorQu -

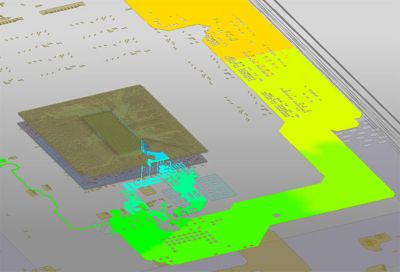

Các trò chơi trong casino RedHawk-SC -

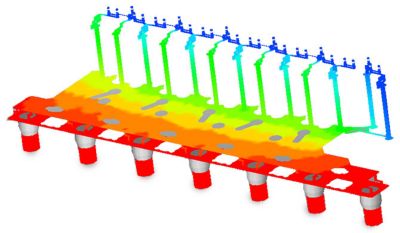

Giải pháp phê duyệt nhiệt Casino -

Top 10 sòng bạc online Totem/Totem-SC -

Đánh bạc trực tuyến Việt Nam Ve

bằng cách cung cấp phần mềm kỹ thuật mô phỏng miễn phí cho sinh viên

bằng cách cung cấp phần mềm kỹ thuật mô phỏng miễn phí cho sinh viên