ANSYS

产品组合

查看所有产品ANSYS

ANSYS 博客

ngày 16 tháng 5 năm 2023

低功耗集成电路 Đánh bạc trực tuyến Việt Nam) , , Đánh bạc trực tuyến Việt Nam 的功耗。有几种方法可用于降低 Đánh bạc trực tuyến Việt Nam 的静态和动态功耗。直流电流和泄漏电流是静态功耗的来源 , ,

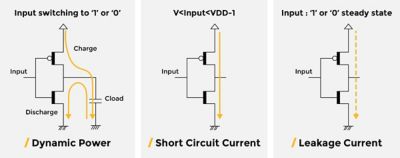

图 1 : 互补金属氧化物半导体 (CMOS)

, 1 同时显示了动态和静态功耗特性。互补金属氧化物半导体 (CMOS)充电使功耗与时钟频率成正比。晶体管在无活动时的功率泄漏会构成静态功耗。

,使用低功耗设计方法来优化设计性能 ,

一种降低设备功耗的方法是在寄存器传输 (rtl) rtl , , ,用于负载电容充电时 , 都会消耗功率。总动态功耗为

PDynamic= Pcap+ Pthoáng qua= (CL+ C) vDD 2f n3

, CL, c 是芯片的内部电容 f 是工作频率 n , , và/cũng không ,锁存器的时钟门控 , Đánh bạc trực tuyến Việt Nam 某些部分的时钟信号可以大幅降低功耗 ,

Đánh bạc trực tuyến Việt Nam , , ,降低功耗。为了有效地运用这一方法 ,

, , , ,信号。这种方法可以大幅降低 Đánh bạc trực tuyến Việt Nam 的局部动态功耗。

, , ,输入的电压岛 , Đánh bạc trực tuyến Việt Nam 的整体功耗。

电压岛技术有一个局限性 电压岛技术有一个局限性 即一旦设计了模块的供电电压 , ,, , , ,可以与频率调节相结合 ,

, 最重要的功耗降低技术是降低芯片的供电电压。动态开关电源在 最重要的功耗降低技术是降低芯片的供电电压。动态开关电源在 finfet , , , ((ulv ) 工艺的发展。

泄漏功耗是前 finfet , 最好使用多 最好使用多 最好使用多 , 每个版本都具有不同的性能/权衡。这样设计人员就可以在时序关键路径中使用快速、泄漏的电路单元 ,

, 有多项技术可用于降低 Đánh bạc trực tuyến Việt Nam 的功耗。通过实施这些技术并使用适当的设计和仿真工具 ,Bắt cờ bạc online mới nhất 2024 RedHawk-SC等工具使工程师能够在各个设计阶段对设计行为进行仿真和预测 从而设计出更节能、具有更长电池使用寿命的低功耗 Đánh bạc trực tuyến Việt Nam。

, , , ,事。一个常见的错误是使用功能验证活动矢量 (acitivity vectơ) , , , 也可以由电源工具 ((

Redhawk-sc 是一款广泛用于 Đánh bạc trực tuyến Việt Nam , 从而帮助解决这一问题。redhawk -Sc 使用复杂的算法对芯片供电网络的行为进行建模 同时考虑到片上电阻、电容和电感等因素。这使 Đánh bạc trực tuyến Việt Nam , ,

如需了解更多信息 ,Bắt cờ bạc online mới nhất 2024 RedHawk-SC主页或查看Chơi casinoCơ sở