-

Hoa Kỳ -

Luật chơi casino -

Ấn Độ -

Pháp -

Chơi casinoPhân -

Italia -

日本 -

대한민국 -

中国 -

台灣

-

Chơi casino , ,

產品系列

查看所有產品-

半導體

系列一覽 -

Đồng hồ Luật chơi casino -

sòng bạc việt nam Exalto: -

Các trò chơi trong Casino -

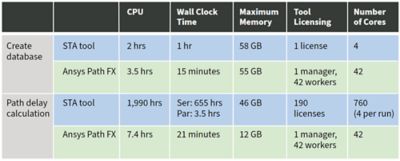

Top 10 sòng bạc online PathFinder-SC -

Chơi xì dách online PowerArtist -

Sòng bạc trực tuyến -

Bắt cờ bạc online mới -

Bắt cờ bạc online mới nhất -

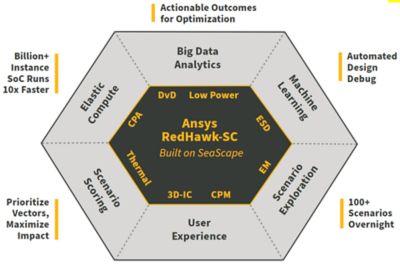

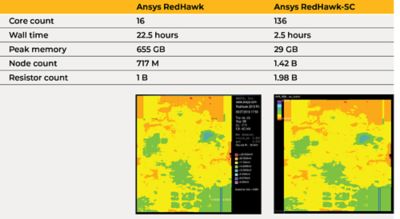

Cờ bạc trực tuyếnNhiệt điện RedHawk-SC -

Cách chơi casino Totem/Totem-SC -

Đánh bài casino VeloceRF

Chơi casino , ,