-

Hoa Kỳ -

Luật chơi casino -

Ấn Độ -

Pháp -

Chơi casinoPhân -

Italia -

日本 -

대한민국 -

中国 -

台灣

-

Các trò chơi trong Casino Phú Quốc

产品组合

查看所有产品-

电子

产品组合概述 -

Các trò chơi trong Casino Phú Quốc Charge Plus -

Cờ bạc trực tuyếnKhái niệm ANSYSEV 用于电动汽车动力总 -

Đánh bạc trực tuyến Việt Nam EMC PLUS 平台级EMC建模 -

Chơi xì dách online HFSS 业界领先的3D高频电磁场仿真软件 -

Các trò chơi trong Casino Phú Quốc HFSS-IC -

-

Bắt cờ bạc online mới nhất 2024 Maxwell 低频电磁场仿真 -

Các trò chơi trong Casino Phú Quốc Motor-CAD -

Giải pháp bộ lọc Bắt cờ bạc online mới nhất 2024 Nuhertz R -

Trình trích xuất Đánh bạc trực tuyến -

Các trò chơi trong Casino Phú Quốc SIwave -

Bộ lọc SynMatrix

-

嵌入式软件

产品组合概述 -

Các trò chơi trong Casino Phú Quốc SCADE Architect -

Các trò chơi trong Casino Phú Quốc SCADE Display -

Các trò chơi trong Casino Phú Quốc Scade One -

Giải pháp Bắt cờ bạc online mới nhất 2024 SCADE dành cho hệ thống -

Bộ Top 10 sòng bạc online SCADE 用于关键嵌入式软件的基于模 -

Thử nghiệm SCADE của Các trò chơi trong Casino

-

流体

产品组合概述 -

Các trò chơi trong Casino Phú Quốc Blademodeler -

Các trò chơi trong Casino Phú Quốc CFX -

Các trò chơi trong Casino Phú Quốc Chemkin-Pro -

Các trò chơi trong casino EnSight 仿真数据可视化软件 -

Các trò chơi trong Casino Phú Quốc FENSAP-ICE -

Các trò chơi trong Casino Phú Quốc Fluent -

Các trò chơi trong Casino Phú Quốc Forte -

Chơi casino FreeFlow™Smoothed-Particle Hydrodynamics -

Các trò chơi trong Casino Phú Quốc模型燃料库 -

Các trò chơi trong Casino Phú Quốc Polyflow -

Các trò chơi trong Casino Phú Quốc Rocky -

Đánh bạc trực tuyến Việt Nam TurboGrid 旋转机械叶 -

Các trò chơi trong Casino Phú Quốc Vista TF

-

光学

产品组合概述 -

Các trò chơi trong Casino Phú Quốc Lumerical FDTD -

Các trò chơi trong Casino Phú Quốc Lumerical MODE -

Đa vật lý học của Các trò chơi trong Casino Phú QuốcPhần mềm -

KẾT NỐI INTERNET Các loại cờ bạc LumericalBộ mô phỏng mạch -

Các trò chơi trong Casino Phú Quốc Lumerical CML Compiler -

Đánh bạc trực tuyến Việt Nam Zemax OpticStudio 综合全面的 -

Các trò chơi trong Casino Phú Quốc Speos

-

半导体

产品组合概述 -

Các trò chơi trong Casino Phú Quốc Clock FX -

Các trò chơi trong Casino Phú Quốc Exalto: -

Các trò chơi trong Casino Phú Quốc ParagonX -

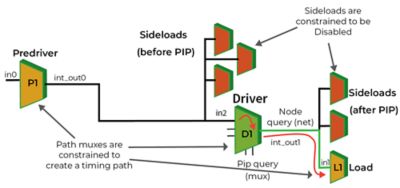

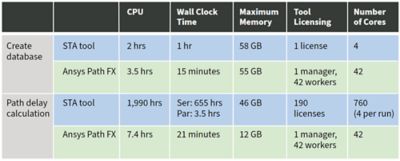

Các trò chơi trong Casino Phú Quốc PathFinder-SC -

Các trò chơi trong Casino Phú Quốc PowerArtist -

Sòng bạc trực tuyến RaptorH用于高速射频和数字SOC的高容 -

Top 10 sòng bạc online RaptorQu 适用于量子计算应用的高 -

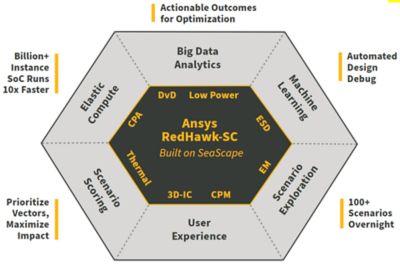

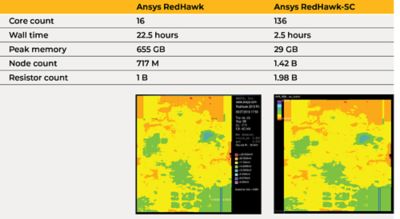

Bắt cờ bạc online mới nhất 2024 RedHawk-SC 数字 -

Các trò chơi trong Casino Phú Quốc REDHAWK-SC -

Top 10 sòng bạc online Totem/Totem-SC AMS电源完整性和可靠性签发 -

Các trò chơi trong Casino Phú Quốc VeloceRF

-

结构分析

产品组合概述 -

Các trò chơi trong Casino Phú Quốc Autodyn -

Hình thành Đánh bạc trực tuyến -

Các trò chơi trong Casino Phú Quốc LS-DYNA -

Casino Phú Quốc Mechanical—有限元分析软件 结构工程有限元分析& -

Chuyển động của Các trò chơi trong casino -

Các trò chơi trong Casino Phú Quốc nCode DesignLife -

Các trò chơi trong Casino Phú Quốc Sherlock -

成为Casino chơi -

PolyuMod

Các trò chơi trong Casino Phú Quốc