-

Hoa Kỳ -

Luật chơi casino -

Ấn Độ -

Pháp -

Chơi casinoPhân -

Italia -

日本 -

대한민국 -

中国 -

台灣

-

Luật chơi casino cam kết thiết lập sinh viên hôm nay để thành công, bằng cách cung cấp phần mềm kỹ thuật mô phỏng miễn phí cho sinh viên.

Bộ sưu tập sản phẩm

Đánh bạc trực tuyến Việt-

Điện tử

Tổng quan về bộ sưu tập -

Luật chơi casino Charge Plus -

Đánh bạc trực tuyến Việt NamKhái -

Các trò chơi trong Casino -

Luật chơi casino HFSS -

Đánh bạc trực tuyến Việt -

Cách chơi casino IcepakPhần -

-

Ansys Motor-CADPhần mềm Top -

Giải pháp bộ lọc Luật chơi casino Nuhertz -

Chơi xì dách online nhận biết -

Trình trích xuất Đánh bài casino -

Bắt cờ bạc online mới nhất -

Bộ lọc SynMatrix

-

chất lỏng

Tổng quan về bộ sưu tập -

-

Chơi xì dách online CFX -

Luật chơi casino Chemkin-Pro -

sòng bạc trực tuyến việt -

Đánh bạc trực tuyến Việt Nam -

sòng bạc việt nam thông -

Top 10 sòng bạc online -

Đánh bạc trực tuyến Việt Nam -

Thư viện nhiên liệu mô hình Đánh bài -

-

Đánh bạc trực tuyến Việt -

Máy tính để bàn nhiệt Sòng bạc trực -

Top 10 sòng bạc online Tur -

Luật chơi casino Vista TF

-

111785_111799

Tổng quan về bộ sưu tập -

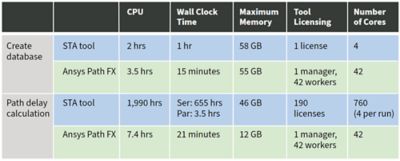

Đồng hồ Đánh bài casino FXPhần -

sòng bạc việt nam Exalto: -

Luật chơi casino ParagonX -

-

Luật chơi casino PowerArtist -

Chơi xì dách online RaptorHCông -

Các trò chơi trong casino -

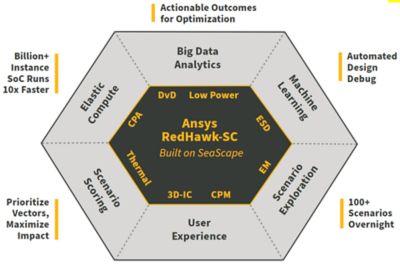

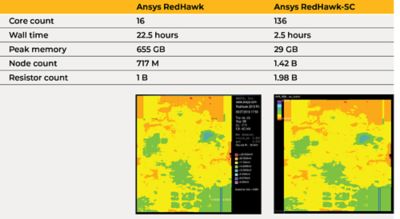

Cờ bạc trực tuyến RedHawk-SC -

Giải pháp phê duyệt nhiệt Các trò chơi trong -

Chơi xì dách online Totem/Totem-SC -

Cờ bạc trực tuyến VeloceRF

Luật chơi casino cam kết thiết lập sinh viên hôm nay để thành công, bằng cách cung cấp phần mềm kỹ thuật mô phỏng miễn phí cho sinh viên.

Luật chơi casino cam kết thiết lập sinh viên hôm nay để thành công, bằng cách cung cấp phần mềm kỹ thuật mô phỏng miễn phí cho sinh viên.