-

Hoa Kỳ -

Luật chơi casino -

Ấn Độ -

Pháp -

Chơi casinoPhân -

Italia -

日本 -

대한민국 -

中国 -

台灣

Tạp chí Chơi casino Advantage

Ngày: 2020

Chơi casino tính toán đàn hồi & Chơi casino dữ liệu lớn giải quyết độ phức tạp xác minh vật lý

bởi Nitin Navale, Quản lý CAD, Xilinx, San Jose, U.S.A.

Thiết kế silicon lớn hơn, phức tạp hơn đang làm căng thẳng phương pháp xác minh và làm chậm thời gian để kết quả và thời gian tiếp thị. Các kỹ sư của Xilinx muốn tận dụng các phân tích dữ liệu lớn để đơn giản hóa luồng xác minh của họ trên các chip hàng đầu và họ đã tìm đến Chơi casino để trả lời.

Nhiều ứng dụng phát triển nhanh chóng ngày nay-có thể là trong trí tuệ nhân tạo, phương tiện tự trị, cơ sở hạ tầng hoặc điện toán hiệu suất cao (HPC)-dựa vào các mảng cổng có thể lập trình hàng đầu (FPGAs) cho hiệu suất và khả năng uốn cong của họ.

The Xilinx XCVU440 can contain up to 400 fabric sub-region (FSR) instances, each with up to 5,000 IP block instances.

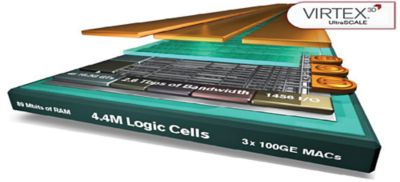

Xu hướng thiết kế silicon-và áp lực tiếp viên của họ đối với hiệu suất và chức năng nhiều hơn-chảy ngược dòng cho các kỹ sư tại Xilinx, công ty Thung lũng Silicon 35 tuổi đáng kính đã phát minh ra lập trình hiện trường. Do kiến trúc lập trình độc đáo của họ, các FPGA luôn là các thiết bị tương đối lớn hơn so với các mạch Chơi casino hợp tiêu chuẩn hoặc hệ thống tùy chỉnh trên chip (SOC), và gần đây là sự bùng nổ của các tính năng mới trên các sản phẩm ACAP Versal của công ty chỉ làm cho chúng lớn hơn và phức tạp hơn

Hơn nữa, điện áp cực thấp dẫn đến lề nhiễu mỏng như dao cạo, do đó sự biến đổi có thể nghiêm trọng. Điều này ảnh hưởng đến thời gian, trong đó biến thể độ trễ thời gian như là một hàm của điện áp đang thay đổi với mỗi nút.

Với hàng tỷ trường hợp và bóng bán dẫn, các thiết kế FPGA này đòi hỏi công suất cao hơn và đủ quy mô và độ bao phủ (nhiều hơn 50 lần so với các phương pháp truyền thống để Chơi casino động và ký hiệu tĩnh) để Chơi casino thời gian thích hợp. Nếu dung lượng công cụ đã bị hạn chế, các nhóm thường không có trong một ngân sách hoặc vị trí thời gian để tiếp thị để có khả năng chạy các mô phỏng dài hơn hoặc nhiều chu kỳ mô phỏng để có được bảo hiểm thích hợp.

Các vấn đề khác cần xem xét bao gồm sự phức tạp của các kỹ thuật và định tuyến gói 2,5D và 3D như Chip-on-Wafer-on-Substrate (COWOS), các ứng suất gây ra lão hóa trên các bóng bán dẫn hiệu ứng trường FIN (FINFES), cũng như như sưởi ấm nhiệt và joule.

Đấu vật với độ phức tạp

Đối mặt với loại phức tạp này, nhóm tại Xilinx đã thích nghi với những thách thức xác minh này. Công ty đã chấp nhận các phân tích dữ liệu lớn và chức năng tính toán đàn hồi, được cung cấp bởi Chơi casino, giúp tăng tốc các thiết kế để hoàn thành trong khi bao gồm chính xác các vấn đề đa vật lý có thể thay đổi đáng kể trên chip.

Một trong những sản phẩm mới nhất của công ty là Xilinx XCVU440, chứa 30 triệu cổng ASIC. Bất kỳ sản phẩm nào từ gia đình này có thể chứa tối đa 400 trường hợp tiểu vùng (FSR), mỗi sản phẩm có tối đa 5.000 trường hợp khối IP.

và

Xilinx không thiếu kinh nghiệm với Chơi casino thời gian tĩnh (STA), nhưng STA hiện đại đang trở thành một thách thức ngày càng tăng với độ phức tạp tính năng lớn hơn ở các nút quá trình tốt hơn. Công ty cần mô hình chính xác cho điện áp cung cấp và phạm vi bảo hiểm rộng hơn.

Theo truyền thống, để thực hiện STA trên một tiểu vùng, nhà thiết kế sẽ tải toàn bộ chip vào công cụ và các vùng hộp đen không cần sự chú ý của họ. Nhưng nó chứng minh ngày càng khó khăn hơn để cô lập hoặc cắt tỉa các phần của thiết kế để thực hiện STA, và việc mở rộng bằng các phương pháp truyền thống đã bắt đầu bị phá vỡ.

Thay vào đó, nhóm đã điều tra một cách tiếp cận hệ thống con nhằm đơn giản hóa thách thức STA và thời gian tốc độ để kết quả mà không ảnh hưởng đến độ chính xác. Họ đã chọn tận dụng Chơi casino SEVECAPE, một nền tảng dữ liệu lớn được xây dựng có mục đích cung cấp chức năng tính toán đàn hồi và dịch vụ tệp/dữ liệu phân tán.

199075_199254

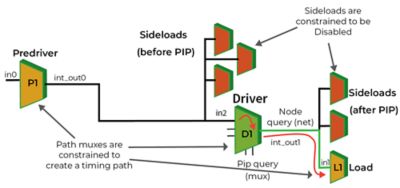

Xilinx có một quy trình nội bộ gọi là chụp thời gian, không chỉ là một quan điểm vật lý của chip, mà còn nhận thức về sự chậm trễ kết nối điểm-điểm của nó. Thay vì thời gian cho toàn bộ thiết kế, thời gian chụp tập trung vào một tập hợp con của các đường dẫn kết nối rất quan trọng.

Sử dụng BEVAPE Chơi casino để mở rộng thiết kế lớn để phân tích thời gian

Nhóm thiết kế bắt đầu bằng cách tải toàn bộ chip vào cảnh biển như một quan điểm vật lý trừu tượng-def và spef (định dạng trao đổi thiết kế, định dạng trao đổi ký sinh tiêu chuẩn) cho các khối cấp độ chip và lef (định dạng trao đổi thư viện) cho các khối IP-và cắt tỉa nó xuống chỉ chứa danh sách chính xác các trường hợp IP mong muốn cho Chơi casino xuôi dòng đó.

Từ đó nhóm có thể xuất khẩu các quan điểm Verilog, DEF và Spef được cắt tỉa có thể được tải vào các Chơi casino khác.

199075_199254

Xilinx đã chạy một thử nghiệm bằng cách sử dụng một FSR duy nhất trên một mini-SOC, có chứa khoảng 375.000 trường hợp khối. Nếu nhóm không lọc nó, nhưng chạy FSR tinh khiết như vậy, bộ đếm thời gian STA của họ sẽ có thể xử lý kích thước của nó.

Nhóm sau đó đã thực hiện thử nghiệm tương tự trên một thử nghiệm đa FSR cỡ trung bình (33 FSR và 32 triệu trường hợp khối). Như trước đây, Sta không thể hoàn thành thiết kế không được bảo vệ.

200242_200416

198861_198918

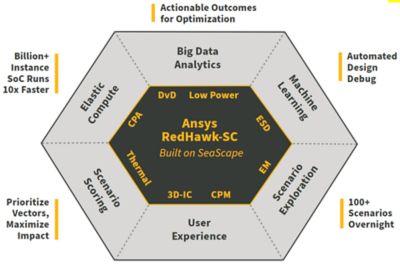

Song song với nỗ lực này, một nhóm Xilinx khác đang sử dụng Chơi casino Redhawk-SC cho EM/IR đăng ký để xem công cụ đó xử lý độ phức tạp và tỷ lệ theo cùng một thang đo đầy đủ. Mục tiêu với ký kết EM/IR là phân vùng chip thành một thứ có thể được xử lý trên máy chủ 1 TB2 và chạy qua đêm, tốt nhất là trong vòng tám giờ.

Để nắm bắt tốt hơn sự gia tăng độ phức tạp của thiết kế tại các nút công nghệ sau này, thiết kế Ultrascale+ Xilinx 16nm có thể được sử dụng làm điểm tham chiếu. Nhóm đã ký tên EM/IR cho toàn bộ con chip đó bằng cách chia nó thành bảy Chơi casino vùng, mất khoảng một tháng cho thiết lập ban đầu.

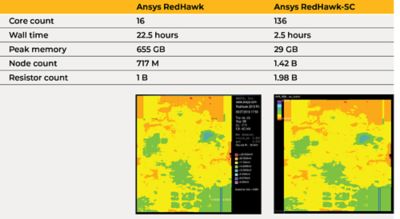

Nhưng không giống như với STA, lần này các kỹ sư Xilinx đã có thể cung cấp dữ liệu không được đặt trực tiếp vào Redhawk-SC, được xây dựng trên đỉnh của cảnh biển và do đó xử lý việc cắt tỉa nguyên bản. Trong thí nghiệm, nhóm nghiên cứu đã Chơi casino một khối địa điểm và đường có kích thước trung bình cho việc giảm IR tĩnh (điện áp DC bị mất trên mạng cung cấp năng lượng do điện trở của nó), so sánh Redhawk cổ điển bốn lõi chạy chống lại

Vì Redhawk-SC đang phân vùng thiết kế trên rất nhiều máy móc hoặc công nhân, thí nghiệm chỉ cần 29 GB bộ nhớ cực đại trên mỗi công nhân, so với bộ nhớ cực đại 655 GB với RedHawk cổ điển. So sánh thời gian đồng hồ treo tường, tính toán phân tán Redhawk-SC đã hoàn thành Chơi casino tĩnh chỉ trong 2,5 giờ, so với 22 giờ đối với Redhawk cổ điển.

Kết quả là một sự cải thiện đáng chú ý về hiệu suất. Redhawk-SC đang cho phép tính toán quay vòng và Chơi casino phối nhanh hơn, và nó làm như vậy với độ hạt mịn hơn so với Redhawk cổ điển.

Chơi casino PATH FX: Tính toán đàn hồi trên độ trễ kết nối quy mô chip

Ngoài việc đóng thời gian STA truyền thống, Xilinx còn có một quy trình nội bộ gọi là Capture thời gian, dành riêng cho kiến trúc toàn lập trình của nó và được điều khiển bởi phần mềm Vivado của công ty. Vivado là công cụ lập trình chip và giống như một luồng thực hiện đầy đủ cho chính nó.

Bởi vì sẽ không thực tế khi Chơi casino các độ trễ này trong khi lập trình chip, thay vào đó, Xilinx đã tính trước chúng trong khi thiết kế chip và sau đó lập trình sự chậm trễ thành Vivado. Do đó, công cụ này đã nhận thức được thời gian kết nối ở các góc PVT khác nhau và sử dụng thời gian đó để tối ưu hóa chip trong quá trình lập trình.

Đối với một công cụ STA truyền thống, mọi đường dẫn xung đột phải được xử lý riêng. Mỗi xung đột có nghĩa là một cuộc gọi riêng để cập nhật thời gian.

Nhóm đã chuyển sang Chơi casino PATH FX để phân tích thời gian đường dẫn quan trọng, có thể tính toán độ trễ pin-to-pin đồng thời trên toàn bộ chip-ngay cả trên các đường dẫn mâu thuẫn. Chơi casino PATH FX hoàn thành kỳ tích này bằng cách áp dụng các ràng buộc cho từng đường dẫn một cách độc lập và sau đó phân phối nhiều đường dẫn trên nhiều công nhân song song.

Xilinx Versal is an adaptive compute acceleration platform (ACAP), a new category of heterogeneous compute devices.

Chơi casino độ trễ dựa trên mô hình mô phỏng cấp độ bóng bán dẫn FX có nghĩa là không mất độ chính xác.

Đây là nơi Chơi casino đàn hồi xuất hiện: Bạn có thể nuôi tất cả các con đường này như những công việc nhỏ cho nhiều máy chủ trên trang trại LSF (cơ sở chia sẻ tải) của bạn.

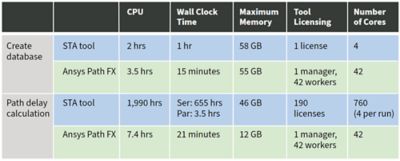

Nhóm đã chạy thử nghiệm trực tiếp so sánh hiệu suất của đường dẫn FX so với công cụ ký kết STA truyền thống của họ trên 95.000 đường dẫn truy vấn. Trong thử nghiệm, việc tạo cơ sở dữ Chơi casino đã mất một giờ thời gian trên đồng hồ tường trong công cụ STA đáng tin cậy của công ty, nhưng chỉ 15 phút trong Path FX với dấu chân bộ nhớ tương tự (~ 55 GB).

Giai đoạn tiếp theo - Chơi casino độ trễ đường dẫn - là nơi đường dẫn FX thực sự tỏa sáng. Công cụ STA đương nhiệm yêu cầu 190 yêu cầu công cụ riêng biệt và gần 2.000 giờ Chơi casino để hoàn thành việc đo lường tất cả các đường dẫn.

Kết quả vượt quá sự mong đợi của nhóm thiết kế. Với cách tiếp cận bán song song của nhóm bằng cách sử dụng công cụ STA truyền thống, họ đã quen với công việc này mất một tuần.

Cấu hình đường dẫn FX (một giấy phép và 42 công nhân) xuất hiện trông hiệu quả hơn về chi phí so với 190 giấy phép của công cụ STA truyền thống.

Lớn, nhanh và chính xác

Để vượt qua các tắc nghẽn mô phỏng hiện đại, Xilinx đã suy nghĩ lại các phương pháp thiết kế của nó và chấp nhận các phương pháp mới bằng cách sử dụng các công cụ Chơi casino. Những công cụ này đã được chứng minh rằng chúng có thể tăng tốc đáng kể thời gian để kết quả mà không phải hy sinh độ chính xác khi nói đến phân tích thời gian và EM/IR.

Với kích thước dữ liệu mô phỏng phát triển đến các kích thước không thể quản lý, Xilinx đã tận dụng cảnh biển Chơi casino và phân tích giảm MAP của nó để cắt tỉa các thiết kế quy mô chip để phân tích thời gian nhanh hơn. Tương tự, Redhawk-SC và Path FX sử dụng việc cắt tỉa và phân vùng thông minh, kết hợp với tính toán dữ liệu lớn đàn hồi, để chia nhỏ từng công việc thời gian của Mammoth EM/IR hoặc kết nối thành một chồng các khối kích thước cắn.

Erfahren Sie, Wie Chơi casino Ihnen Helfen Kann

Erfahren Sie, Wie Chơi casino Ihnen Helfen Kann

Kontakt

Danke für Die Kontaktaufnahme

WIR SIND HIER, UM IHRE FRAGEN ZU ANH Ein*e Mitarbeiter*Trong Unseres Chơi casino-Verkaufsteams Wird Sich in Kürze Mit Ihnen trong Verbindung Setzen.